고정 헤더 영역

상세 컨텐츠

본문

"AXI4-Lite Interface"

# AXI4-Lite Introduce

버스트 액세스 기능이 없는 AXI의 하위 세트로서, 전체 AXI4 인터베이스보다 간단한 인터페이스입니다.

# AXI4-Lite interface signals

AXI4-Lite 인터페이스는 Read Address, Read Data, Write Address, Write Data, Write Response의

5개의 Channel로 구성됩니다.

//AXI4의 Read Transaction( Read Address, Read Data)은 아래 그림에 나와 있습니다.

Read는 마스터가 Address를 주면, 슬레이브가 Data를 마스터에게 보냅니다.

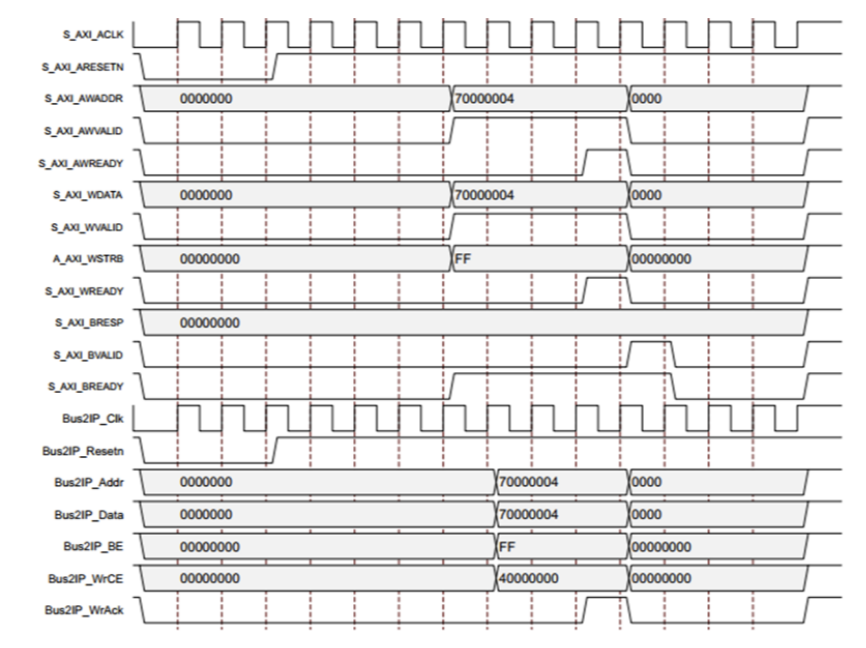

//AXI4의 Write Transaction( Write Address, Write Data, Write Response )은 아래 그림에 나와 있습니다.

Write는 마스터가 Address와 Data를 보내면, 슬레이브는 Response를 마스터에게 보냅니다.

위 그림은 AXI4의 Burst전송을 나타내는 것이고 AXI4-Lite에서는 지원하지 않습니다.

# AXI4-Lite Interface의 각각의 신호를 나타내는 설명

Global Signals

| Name | Direction | Description |

| ACLK | M | Clock source. |

| ARESETN | M | Global reset source, active low. |

Read Address Channel

| Name | Direction | Descrption |

| ARADDR | M | Read Address (usually 32-bit) |

| ARCACHE | M | 메모리 타입. 일반적으로 슬레이브인 경우 이 값을 무시. 마스터인 경우는 일반 비 캐시가능, 수정가능 및 버퍼가능(0011)으로 트랜잭션 생성. |

| ARPROT | M | 보호 타입. 일반적으로 슬레이브인 경우 무시. 마스터는 보통, 보안 및 데이터속성(000)으로 트랜잭션 생성. |

| ARVALID | M | Read address valid signal. 마스터가 Read Address와 그 제어신호를 허용할 때 그 신호를 생성. |

| ARREADY | M | Read address ready signal. 슬레이브는 주소와 제어신호를 받을 수 있을때 이 신호를 생성. |

Read Data Channel

| Name | Direction | Description |

| RDATA | M | Read Data (32-bit only). |

| RRESP | M | Read response. 데이터 읽기 전송 상태를 나타내는 신호. |

| RVALID | M | Read valid. 슬레이브가 데이터 읽는것을 허용할 때 나타내는 신호. |

| RREADY | M | Read ready. 마스터가 데이터를 읽고, 응답하는 것을 받아들일 수 있을때 나타내는 신호. |

Write Address Channel

| Name | Direction | Description |

| AWADDR | M | Write address, usually 32-bits wide. |

| AWCACHE | M | Memory type. 슬레이브에서는 사용하지 않고, 마스터에서는 일반 비 캐시가능, 수정, 버퍼가능일(0011) 때 트랜잭션을 생성. |

| AWPROT | M | Protection type. 슬레이브에서는 사용하지 않고, 마스터에서는 일반, 보안, 데이터 속성(000)일 때, 트랜잭션을 생성. |

| AWVALID | M | Write address valid. 마스터가 Write Adreess와 제어 신호를 받아드릴수 있을 때 이 신호를 생성. |

| AWREADY | M | Write address ready. 슬레이브가 Write Address 와 그 제엇니호를 받을수 있을 때, 이 신호를 생성. |

Write Data Channel

| Name | Direction | Description |

| WDATA | M | Write data (32-bit only). |

| WSTRB | M | Write strobes. 4byte의 Write Data를 나타내는 4bit 신호. 슬레이브는 모든 byte가 유효하다고 가정함. |

Write Response Channel

| Name | Direction | Description |

| BRESP | M | Write response. 쓰기 트랜잭션의 상태를 나타내는 신호. |

| BVALID | M | Write response valid. 슬레이브는 버스에서 쓰기 승인이 유효할 때 이 신호를 생성. |

| BREADY | M | Response ready. 마스터는 쓰기 승인을 받아들일 수 있을 때 이 신호를 생성. |

@ Clock과 Reset

Clock신호 ACLK와 Active-low의 비동기 reset신호 ARESETN은 AXI4의 Global Signal이다.

모든 AXI4 신호는 클럭의 rising edge에서 활동하고 모든 신호 변화는 rising edge후에 발생해야 한다.

@ HandShake Process

모든 다섯가지 트랜잭션 채널들은 주소,데이터,제어정보를 전송하기 위해 VALID/READY의 핸드셰이크 과정을 사용한다.

두방향의 제어 매커니즘은 마스터와 슬레이브 둘 사이에서 정보가 이동하는 컨트롤을 의미한다.

Source information은 address, data, control information이 가능할 때 VALID 신호를 생성한다.

Destination information은 information을 받아들일 수 있을 때, READY 신호를 생성한다.

핸드셰이크 과정은 rising edge에서 해당 Channel에 VALID와 READY신호가 둘다 선언되면 완료된다.

# AXI4-Lite Read Transaction

1. READ ADDRESS CHANNEL에서 마스터는 address를 넣는다.

ARVALID(주소를 보내는 것을 허용하는 신호)와 RREADY(마스터가 슬레이브로부터 데이터를 받을 준비가 된 신호)

2. 슬레이브는 ARREADY(버스에서 주소를 받을 준비가 된 신호)를 선언한다.

3. ARVALID와 ARREADY두 신호가 함께 활성화 되면, rising edge에서 핸드셰이커가 발생한다.

그 후 마스터와 슬레이브는 ARVALID와 ARREADY를 비활성시킨다.

(이 지점에서 슬레이브는 요청한 address를 받는다.)

4. READ DATA CHANNEL에서 슬레이브는 요청된 Data를 넣고, RVALID(데이터를 보내는 것을 허용하는)를 선언한다.

슬레이브는 또한 RRESP로 응답을 할 수 있다. (하지만 지금 아래의 그림에서는 보여지지 않는다.)

5. RREADY와 RVALID가 둘다 활성화 된 후, 다음 rising edge에서 트랜잭션이 완료된다.

RREADY와 RVALID는 비활성화 된다.

**Master Signals : ARADDR, ARVALID, RREADY

**Slave SIgnals : ARREADY, RDATA, RVALID, RRESP

# AXI4-Lite Write Transaction

1.WRITE ADDRESS CHANNEL에서 마스터는 address를 넣고, WRITE DATA CHANNEL에서 마스터는 data를 넣는다.

동시에 각각의 채널에 있는 AWVAILD(주소를 보내는 것을 허용하는 신호) WVALID(데이터를 보내는 것을 허용하는 신호)를

활성화 시킨다. 그리고 BREADY(wirte전송에 대한 응답을 받을 준비 하는 신호)를 활성화 시킨다.

그리고 WSTRB는 1byte를 나타내는 신호로써 ff값을 넣는다.

2. 슬레이브는 WRITE ADDRESS CHANNEL과 WRITE DATA CHANNEL 각각의 채널에서

AWREADY와 WREADY신호를 보낸다.

3. 각각의 채널에서 VALID와 READY신호가 동시에 나타난 이후로 두 채널 모두 핸드셰이크가 발생하고

관련이 있는 VALID신호와 READY신호는 비활성화 된다.

(두 핸드셰이크가 발생한 후, 슬레이브는 write address와 write data를 한다.)

4. WRITE RESPONSE CHANNEL에서 슬레이브는 BVALID(응답을 유효화 하는 신호)를 활성화 한다.

(이 경우 BRESP은 'OKAY'를 나타내는 2'b00값이 된다.)

5. READY와 VALID신호가 WRITE RESPONSE CHANNEL에서 둘다 high가 되면

다음 rising edge에서 트랜잭션은 완료된다.

**Master Signals : AWADDR, AWVALID, WDATA, WSTRB WVALID, BREADY

**Slave Signals : AWREADY, WREADY, ,BVALID, BRESP

NOTE:

Write Address와 Write Data Channel에서 두 Handshakes 반드시 동시에 일어나지 않아도 됩니다.

그러나 AXI4사양에 따라서 슬레이브가 write response를 보내기 전에 두가지가 모두가 완료 되어야 합니다.

# RESPONSE의 값

AXI4-Lite에서는 RESPONSE의 값이 2'b00입니다.

| RRESP[1:0], BRESP[1:0] | Response |

| 2'b00 | OKAY (Normal access success) |

| 2'b01 | EXOKAY (Exclusive access oaky) |

| 2'b10 | SLVERR(Slave error) |

| 2'b11 | DECERR (Decode error) |

[스크랩 본문] https://www.realdigital.org/doc/a9fee931f7a172423e1ba73f66ca4081

Welcome to Real Digital

Digital Systems Topic: AXI4-Lite Interface AXI4-Lite Interface Introduction to AXI4-Lite Introduction to AXI4-Lite (Advanced Extensible Interface) Advanced eXtensible Interface 4 (AXI4) is a family of buses defined as part of the fourth generation of the A

www.realdigital.org

'programming > AXI' 카테고리의 다른 글

| [AXI] AXI protocol에 대하여...(1) (1) | 2020.08.13 |

|---|---|

| [AXI] AXI버스란? (0) | 2020.08.03 |

| [AXI] ARM의 AMBA BUS 란? (0) | 2020.08.03 |